BinaryAdder 二进制加法器

本文核心词:IC,Verilog

加法器:数字计算机处理很多信息或者任务时,会进行大量的运算操作,而大部分的运算操作中最基础的运算操作则是加法操作,常见的则是2组二进制数据的相加运算。以4位全加器位例,通过使用Verilog对该电路采用三种不同的设计方法,进行计算速度的比较和运算原理的说明:

4位全加器

4位全加器运算原理:全加器在进行运算时,从右往左依次进行,A0-A3、B0-B3,C0将在同一时刻打入各自的全加器输入口,那么相应的S0-S3的输出也会产生相应的数值,而在此时产生的数值时一个不定状态,即错误结果;当经过一定的时间后,S0-S3才会产生正确、稳定的结果,而这个一定的时间则正是该模块的延时,即C0打入第一个全加器后产生的C1打入第二个全加器产生的C2....一直到产生C3打入最后一个全加器所经过的时间,在这个时间之后,才会输出正确、稳定的结果。

4位全加器模块图

4位全加器电路图

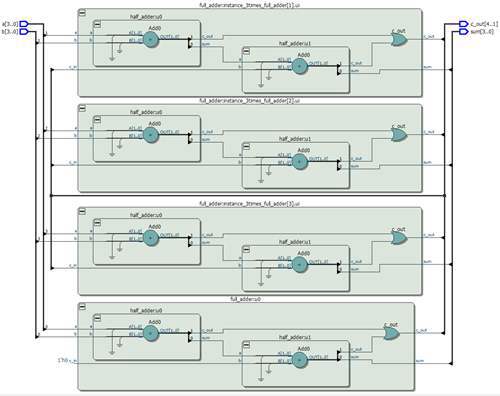

设计方法1:使用常规的2个半加器组合成一个1位全加器,再使用4个1位全加器构成一个4位全加器;

4位全加器门级电路图

从全加器运算原理和门级电路图可知,C_out经过每一个全加器会经过一个与门和一个异或门,假设时间为2ns,那么一个4位全加器计算出完整结果则需要8ns的时间;

有没有什么办法可以使得运算速度快一点呢,除了改变器件的物理结构除外?这里提供有两种办法会使得计算速度快一点;

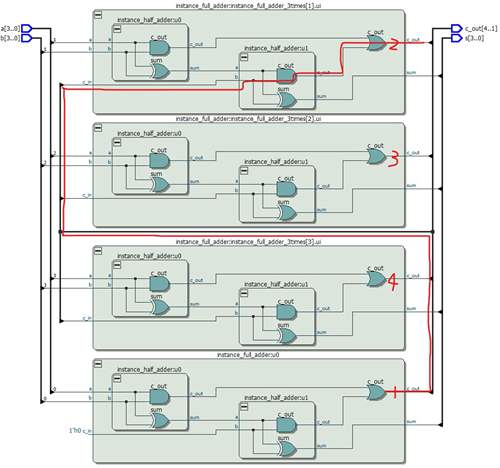

设计方法2:(下图位置1)使用4个半加器同时产生进位输出(c_out)和半加器加和结果(sum)分别用Q、P表示,(下图位置2),然后使用P、Q经过一定的逻辑门同时产生全加器的进位输出(C),(下图位置4)最后将P(半加器加和结果)和C(全加器进位输出)通过异或逻辑门,获得输出结果(sum);

4位全加器门级电路图

上图设计可知,假设输入数据同时通过4个半加器所用时间为1ns,产生全加器进位输出所用时间为1ns,产生最终结果所用时间为1ns,那么一个4位全加器计算出完整结果则大概需要3ns的时间;

设计方法3:先使用2个1位全加器(module1)计算低两位的加和结果和进位输出,再使用另外两组2位全加器(module2、module3)分别计算当进位输入为1、0时候的加和结果,当(module1)的进位输出得到后,选择器选择(module2、module3)中的对应的加和结果输出即可;

4位全加器门级电路图

上图设计可知,假设输入数据同时通过2个1位全加器所用时间为3ns,下面的2位全加器进位输出所用时间为1ns,通过选择器选择产生最终结果所用时间为1ns,那么一个4位全加器计算出完整结果则大概需要5ns的时间;